在上一篇文章中,我们讨论了为了减少二次谐波失真,需要对称的PCB布局 .

在本文中,我们将看到,如果没有适当的解耦,我们就无法从高速运算放大器中提取最大的线性性能。此外,我们将讨论简单地重新布置去耦电容器会影响高速放大级的失真性能。

不良的电容去耦会增加失真印刷电路板的电源和接地导体确实表现出一些电感。如果我们试图通过电源和接地导体直接提供设备的高频电流,这种电感会引起问题。

回想一下,电感器上出现的电压降与电流的变化率成正比。因此,在更高的频率下,电源和接地导体之间会出现相对较大的电压降,我们将无法向IC提供恒定的电源电压。

使用高速运算放大器时,电源电压的变化将取决于信号,因此,线性性能将显著降低。

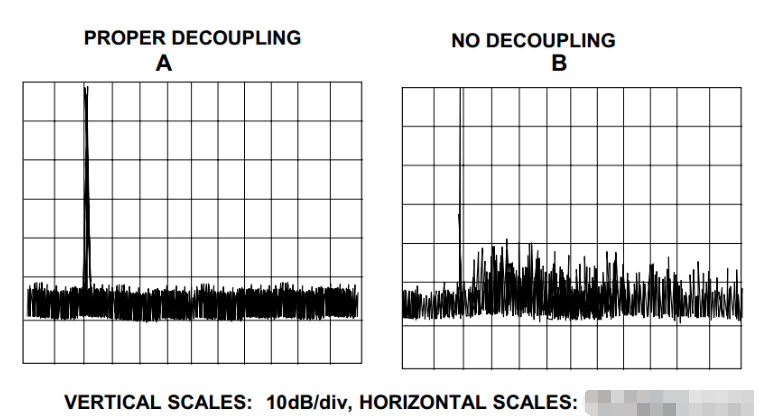

为了解决这个问题,我们把去耦电容器放在运算放大器电源引脚附近。去耦电容器作为电荷源,提供高频电流,显著降低电源电压的变化。下图显示驱动100Ω负载的AD9631运算放大器输出端的频率含量。

图1AD9631运算放大器的光谱输出,具有适当的去耦(左)和不去耦(右)。图片由模拟设备 .

如您所见,通过适当的解耦,失真分量将显著减少。

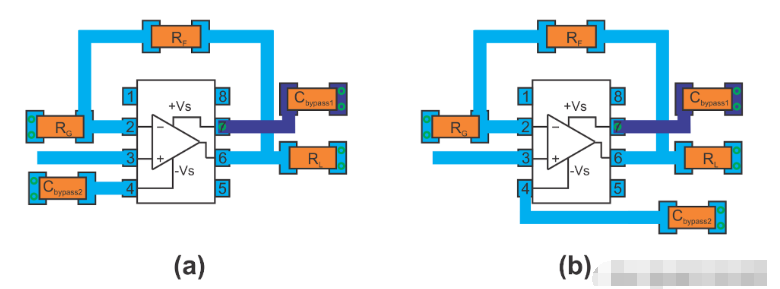

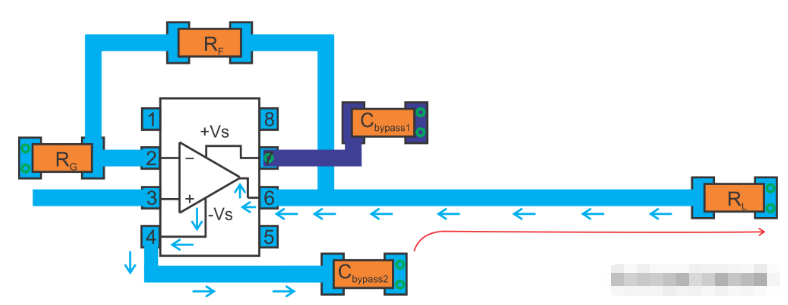

使电容器接地端子远离运算放大器输入PCB版图是优化高速电路板畸变性能的关键因素。考虑下面所示的在SOIC封装中使用运算放大器的非反转放大级的布局示例。

在这些例子中,所有元件都放置在电路板的顶部,只有正极轨道(C)的旁路电容器旁路1)在底部。我们假设有一个绿色的地板,或者说是一个接地的平面。

图2负轨旁路电容器位置不同的两个电路图。

正如你所看到的,这两种布局完全相同,除了放置负轨的旁路电容器(C旁路2). 而左边的布局是C的底边旁路2靠近运算放大器输入端,右侧的布局试图使该端子靠近负载,远离运算放大器输入端。

图2(b)中的布局可以获得更好的失真性能。

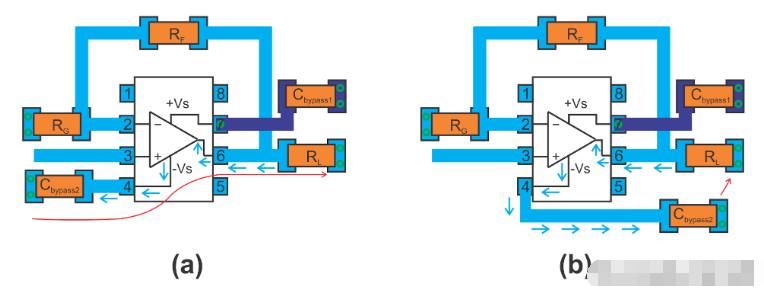

注意回流路径为了理解为什么图2(b)中的布局显示较低的失真,考虑当施加到负载的信号具有负极性(即C)时流过接地层的回流电流旁路2正在提供负载电流

当输出信号的极性为负时,从负载引出的电流流过顶层跟踪和运算放大器电路,如图3中蓝色箭头所示。

图3与图2中的图相同,但用蓝色箭头显示当前流。

我们知道高频回流电流直接在信号轨迹下方流动使循环面积最小化。因此,图3(a)中布局的返回电流应该遵循与红线所示类似的路径。

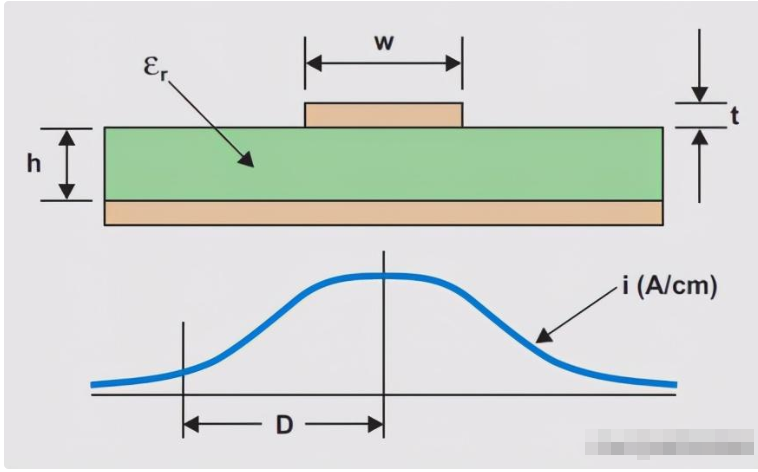

然而,需要注意的是,尽管大部分回流电流直接在信号轨迹下方流动,但它仍然可以在地平面上略微扩散,如图4所示。

图4高频回流分布。图片由Segera Davies .

因此,在图3(a)中的布局中,回流电流会干扰运算放大器输入端的电压。耦合到运算放大器输入端的错误信号将与信号相关,因此,将在运算放大器输出端造成失真。由于信号相关的误差电压只出现在输出电压的一个极性(负极性)时,它将主要增加二次谐波失真。

在图3(b)中,返回电流将在接地层上选择什么路径?

同样,信号轨迹正下方的路径(蓝色箭头下方)将提供尽可能低的电感。但是,在这种情况下,旁通盖的接地侧非常接近负载的接地端子。因此,与电感最小的路径相比,3(a)中红色箭头所示的路径可以提供非常小的电阻。实际上,回流电流会选择阻抗最小的路径(路径电感和电阻都要考虑)。

为了确定返回电流的精确分布,我们需要模拟工具;然而,我们可以推断出一部分回流电流将围绕红色箭头流动,而相对较小的电流将在蓝色箭头下方流动。由于在信号轨迹下流动的电流相对较小,我们可以期望在电路的敏感节点(运算放大器输入端周围)下方有一个“更安静”的接地。

保持旁路盖的接地端远离运算放大器输入端是减少谐波失真的一种有效技术,通常在不同芯片制造商的不同技术文件中推荐使用。

如果负载远离运算放大器的输出呢?让我们再看一个例子,其中负载位于离运算放大器输出一定距离的地方,如图5所示。

图5我们的例子运算放大器电路,但负载远离运算放大器输出。

同样,我们应该保持旁路电容器的接地端远离运算放大器的输入端。电容器应放置在靠近运算放大器电源引脚的地方,其接地端子靠近运算放大器输出端。

相当大一部分回流应遵循上述低电阻路径,导致下图中红线所示的回流路径。

为了从高速运算放大器中提取最大的线性性能,需要适当的解耦。此外,旁路电容器的接地侧应靠近运算放大器输出端,远离其输入端,以便在电路的敏感节点下(在运算放大器输入端周围)有一个“更安静”的接地。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。