他们说时机决定一切。当谈到数字系统中的信号完整性时,“他们”并不遥远。即使在模拟系统中,普遍的看法是越短越好。两个学科都利用迹线长度作为提高性能的一种手段。在数字方面,我们关心的是保持大量的信号与时钟同步,而模拟网络使用延迟线有其独特的原因。

哪一个是对的?

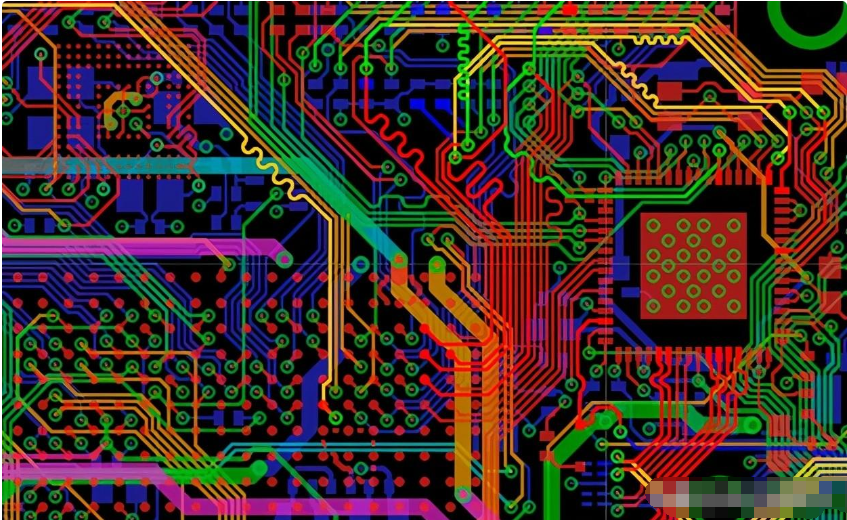

精美复杂的PCB板设计。资料来源:Autodesk

让我们从数字域开始。我们喜欢想象一个行军乐队随着鼓点的节拍移动和演奏。大低音鼓发出低沉的拍子,称为“一”。一切从一开始。陷阱鼓手添加他们的味道在后面拍和提供填充。这样,你就得到了一,然后是零。号角演奏者和其他人轮流演奏和休息这两个事件,以发挥旋律。你有数据了。

鼓芯是乐队的计时元件。节奏部分为曲调打下了一个凹槽。在印刷电路板上,定时工作制当然是名称中带有“CLK”的一个或多个网络。请注意,当在示意图中使用时,CLK是时钟网络的常用符号。这钟从不报时。与此同时,公交车上的其他成员也有休息的时间。

噪音从哪里来?事实上,时钟是连续切换的,而其他时钟是间歇的,这就是为什么时钟是噪声的。开关速率由控制器芯片或外部振荡器决定。在晶体周围收集电容器和/或电阻,以及仔细的布线,是获得清晰脉冲的努力的一部分。

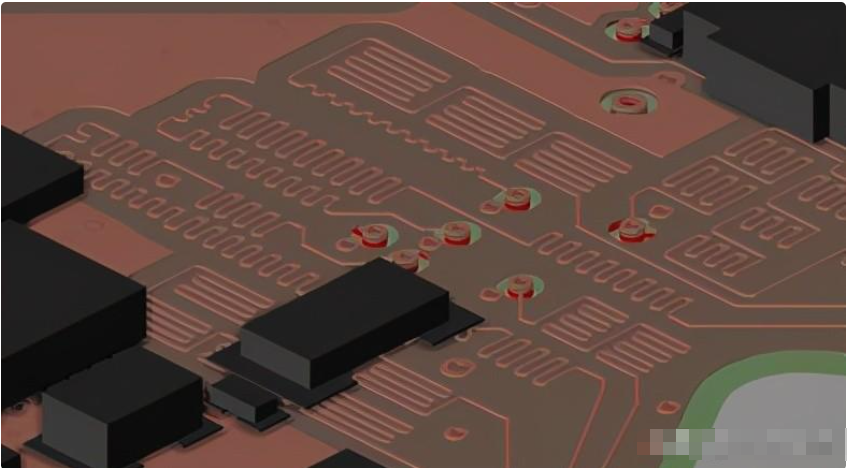

图1.图片来源:显示长度匹配方案的内部层

当我们谈论双数据速率(DDR)时,作用于下拍和后座的不是时钟而是其他信号。这会让你觉得那些噪音会是时钟的两倍,如果不是所有的休息时间都是这样的话。我们严格关注DDR信号从低电压状态到高电压状态的阈值。

请注意,“低”通常意味着零伏,而高可以是1V到5V之间的任何值。相对来说都是低电压。因为电压波动越大,噪音就越大。我们喜欢在1.8V电压下运行晶体,而其他电路则在0V和3.3V之间切换。

电源–为什么PCB上有这么多电压域?一个完整系统的电源树可能从墙上插座的110/220VAC开始,然后在使用电源电路转换为直流电时降压。电路可以是用变压器、电感器、电容器、电阻器和二极管放在电路板上并布线的部件的集合。

变压器根据每侧绕组的数量来降低或增加电压。电感器和电容器使电流平滑,而电阻器则用来将功率分成各种较小的电压。最后,二极管保持电流通常朝一个方向流动。电源模块之所以受欢迎,是因为它们冒着设计所有这些都要通过UL和FCC法规的风险。保险商实验室(UL)是一个组织,负责证明您的产品不会轻易着火,而联邦通信委员会(FCC)则确保它能很好地与其他电子产品配合使用。这两项都是必要的商业审批。

移动设备将使用已经是直流电的电池或“墙疣”电源,并将VBAT或VIN分为1.2、1.8、2.5、3.3、5.0和9或12VDC。这一切都取决于成分组合。即使每一个部件都使用相同的电压电势,他们也倾向于想要一个独立的轨道。

低电压开关更快,因为它的变化幅度较小。低电压也更容易受到足够的噪声的影响,从而很难判断信号是代表高还是低的状态。当整个范围是一伏时,毫伏加起来很快。就像铜管需要喘息,这样我们才能听到木管乐器和长笛的声音。

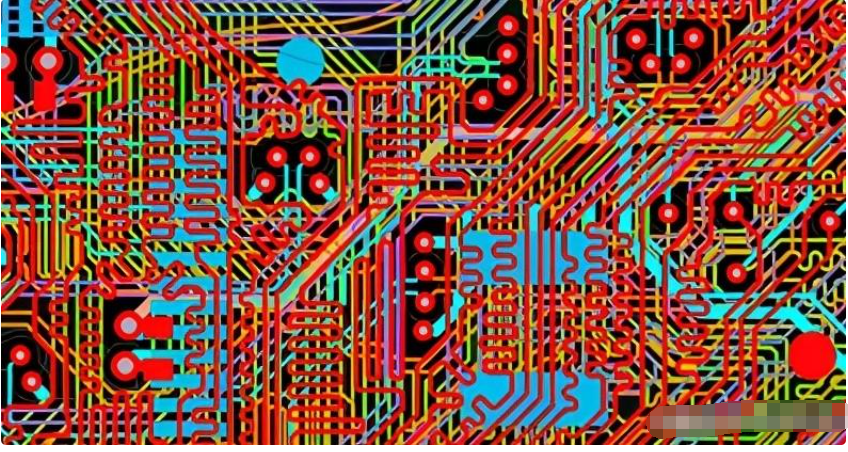

图片来源:单端或差分,跟踪使用蛇形曲线来满足时间预算。

那么,我们在哪里?啊,是的,各种各样的总线,每种不同类型的母线在许多可能的电压波动中运行。低电压信号需要它们的空间,这样它们就不会被高电压设备搞糊涂。

数据包沿着线路发送,然后在传输设备发送一个由1和0组成的快速流时暂停,这些数据流表示已传输的字节总数。一个字节中的位数和其他框架,如是否有停止位、奇偶校验和双工,都是由固件确定的。

通过这种方式,接收器端知道这个带有字节数的数据突发,并对接收到的字节数进行计数。如果发送的号码与收到的号码相匹配,则接收器将继续监听更多的号码。如果鈥渃赫克苏姆鈥 不一样,接受者说,鈥渉老了,把最后一个包裹再寄一次。

丢包怎么办?丢包是个坏消息,因为它们会减慢系统的速度。即使发送冗余数据不影响实际程序的运行,它仍然会占用时钟周期。每一个时钟周期都会消耗一小部分能量,并产生一点噪声脉冲。不必要的能源使用和噪音的产生使得系统的效率大大降低。适当的信号定时可以降低误码率,使整个系统运行得更好。

孤立地看,信号完整性依赖于两个主要因素,定时和阻抗。时间是长度的函数,但不是严格意义上的。从一片硅片连接处到另一片硅的飞行时间考虑了整个路径。金或铝丝键有一定的传播速度。基板上使用的陶瓷材料比PCB上使用的典型FR4材料产生的延迟更小。信号在外层传播得更快,甚至在空气中传播得更快。总长度对你不利,因为轨迹总是有电阻,电容。还有电感。

例如,无线****机可能具有模拟不同长度的吉他电缆的设置。这个想法是为了补偿每英尺导线引起的高频衰减量。在低音,这并不重要,但一些吉他手认为电缆是他们的音调的一部分。高速数码更像是吉他手。

图2:图片来源:绑在吉他踏板板的底部,无线接收器有一个可变的低通滤波器,用一根典型长度的电缆来模拟。

信号的高频部分是数据所在的地方。其他具有更高振幅的低频信号有产生基频谐波的趋势。这些杂散信号是那些将锁定在总线的高频信号上的信号。这样一来,一个1兆赫的信号就能摧毁一个2.5千兆赫的信号。当有一个轨迹违反阻抗规则时,光靠间距是不够的。

真正影响你的不是每秒的周期,而是各种信号的上升和下降时间。边缘速率是信号完整性的主要关注点之一。这就是整体设计的重要性所在。一块板上有很多不同的信号,其中任何一个都可能受到其他任何信号的影响。返回路径通常是信号中被忽略的部分。所有输电线路都有接地。一个设计拙劣的跟踪可能会破坏其他所有跟踪。

Vias——一种必要的邪恶;谨慎使用最大的问题之一是痕迹在哪里发生了变化。通孔造成阻抗不匹配。它们造成的痛苦会被粘在外层而被抵消。长时间暴露的痕迹会导致更多的辐射,这从电磁干扰(EMI)的角度来看是有问题的。还记得联邦通信委员会吗?他们不喜欢百代。

再加上一个事实,大多数公共汽车都有相互交叉的痕迹。使所有轨迹长度匹配得足够好以满足设计约束是最后一道稻草。我们使用过孔,但只使用必要的过孔,这通常意味着在连接的每一端都有一个通孔。

蛇纹石最好保持在这些内层。单个字节通道希望使用相同的路由层,以便所有信号完整性问题都得到均衡。去掉变量使定时和阻抗计算更简单。长度匹配从使长帐篷杆尽可能短开始。然后,可以调整时钟,使最长的跟踪符合要求。在那之后,将有其他的痕迹,必须延长到最小,以满足时钟减去计时预算。同步信号一起播放效果更好。

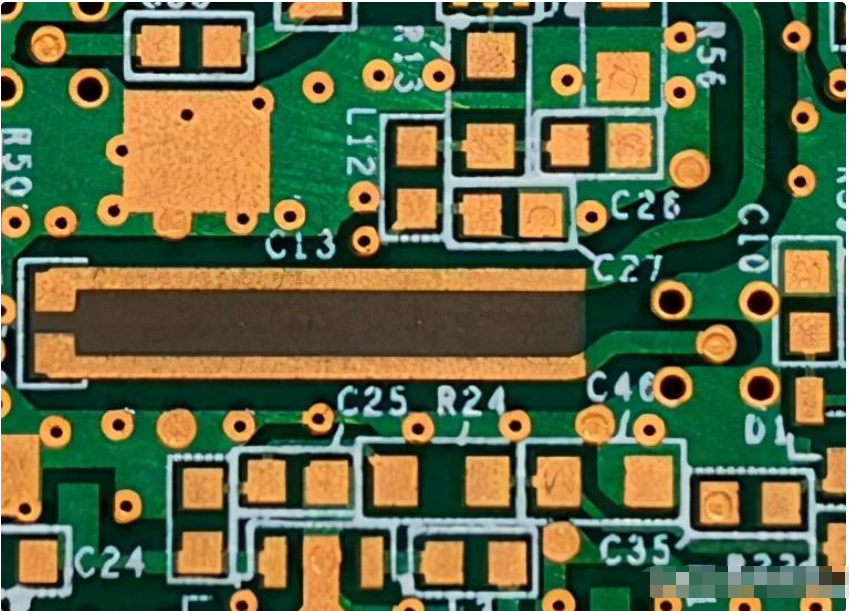

模拟电路板设计中的蛇形模拟更关心频率。想象一下长号的滑动或喇叭每个阀门上的管道长度。每个长度的共振频率提供不同的音符。模拟电路中的延迟线有助于使波形与系统其他部分协调一致。我们关心的是信号的音调,而不是它是开还是关的二进制问题。

放大器可能需要一点预失真,以补偿其环境。为了知道什么会有帮助,对信号进行采样和评估。主射频信号需要等待校正技术,以便计算和插入重点。有很多方法可以做到这一点,但他们通常只需要一点点蛇形,以保持一切同步,然后到天线。

图片来源:这个轨迹配置有一个非常相似的幻灯片长号。目的很相似。

一种方法使用硬件中设置的可变延迟量。一对传输线并排运行时,可以在这两条线路上放置一个电阻或电容器,使电路在最佳的空间/时间内完成。技术人员会在不同的地点缩短这两个痕迹,直到他们找到最佳位置。然后,他们会焊接跨接导线,并切断剩余的短管。

当然,很多这一切都是通过数字信号处理完成的。芯片、电路板和软件的组合将用于校正信号以获得最佳性能。延迟线是许多PCB设计 .

无论您需要调整什么,您的供应商都可以帮助您正确选择材质和跟踪几何图形,以满足您的设计目标。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。