在解决信号的第12部分中,我们看了一个电源噪声设计示例,以讨论在试图提高系统的PSR时,哪些电源是最关键的。从这个例子中,我们提供了保持低电源噪声的最佳实践和系统总体噪声性能的调试技巧。

在我们系列的第11部分,我们讨论了电源噪声主题,包括什么导致电源噪声以及它如何影响模数转换器(ADC)。我们还介绍了电源抑制(PSR)作为描述电源在抑制噪声方面的有效性的方法。最后,简要分析了电源噪声对不同ADC电源的影响。

在本文中,我们将以一个使用ADS127L01评估模块(EVM)的设计实例继续讨论电源噪声。这个例子将有助于说明在试图提高系统的PSR时,哪些电源是最关键的。最后,我们将讨论保持低电源噪声的最佳实践以及改善系统整体噪声性能的调试技巧。

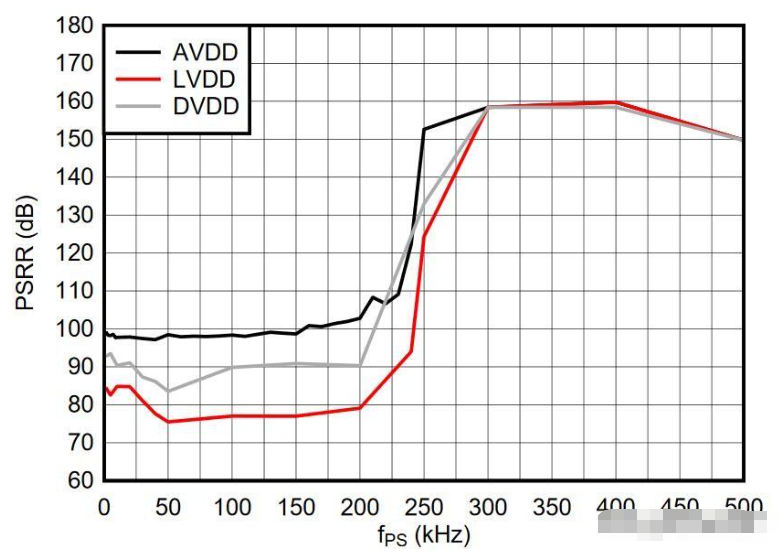

AVDD,DVDD还是LVDD:哪个最重要?在第11部分中,我们研究了德州仪器(TI)使用的每个电源的PSR比率(PSRR)ADS127L01(如图1所示)。像大多数adc一样,ADS127L01同时使用模拟和数字电源(分别是AVDD和DVDD)。我们之所以选择这个设备作为我们的讨论对象,是因为它还需要第三个称为低压差分电源(LVDD)的电源。LVDD直接为ADS127L01中的δ-西格玛调制器供电。LVDD电源可由内部低压差调节器(LDO)(连接至AVDD)或外部LVDD电源提供。正如您在本文后面将看到的,在外部使用噪声源驱动LVDD将对ADC噪声性能产生最不利的影响。

图1TA=25°C, AVDD = 3.3V, VREF = 2.5V, HR Mode, INTLDO = 1

从图1可以看出,LVDD最容易受到耦合噪声到ADC输出的影响,因为它的PSRR在三个电源中最低。LVDD对噪声最敏感,因为它直接为delta-sigma调制器供电,后者又直接控制模拟输入到数字输出的转换过程。相对而言,AVDD为剩余的模拟电路供电,包括产生主偏置电流,但这对转换结果的直接影响较小。为ADC的数字核心供电,DVDD对转换结果的影响最小,因为调制器输出在到达数字抽取滤波器时已经是二进制的。对于需要多个电源的设备,应优先选择最直接为delta-sigma调制器供电的电源,通常是AVDD。

为了说明在现实世界中使用噪声源驱动调制器的效果,我们进行了一个ADC输入短路噪声测量上ADS127L01评估模块以下四种情况下的EVM:

清洁AVDD、LVDD和DVD上的电源(无波纹)。

AVDD = 3 V + 1-kHz, 100-mVP ripple, clean LVDD and DVDD.

LVDD = 1.825 V + 1-kHz, 100-mVP ripple, clean AVDD and DVDD.

DVDD = 1.8 V + 1-kHz, 100-mVP ripple, clean AVDD and LVDD.

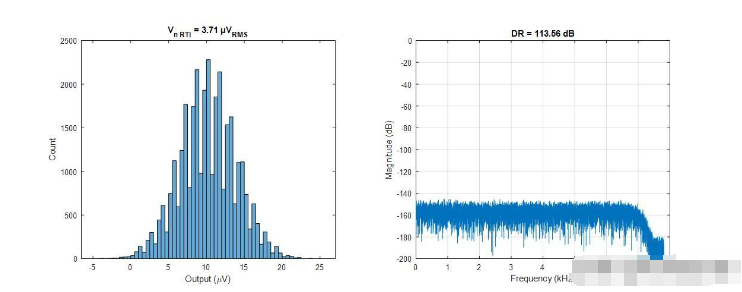

在每种情况下,我们将ADC输入端短接在一起,将其偏置到中间电源(1.5 V),并计算相对于ADC满量程的最大可实现信噪比。我们将此结果称为ADC的动态范围。表1ADS127L01产品介绍(PDF)列出了ADC每种操作模式和数据速率的典型噪声性能。该测试是在极低功率模式下进行的,采用4-MHz时钟输入,使用过采样率=256的宽带2数字滤波器。根据表1,我们预计在这些设置下的动态范围约为114 dB。

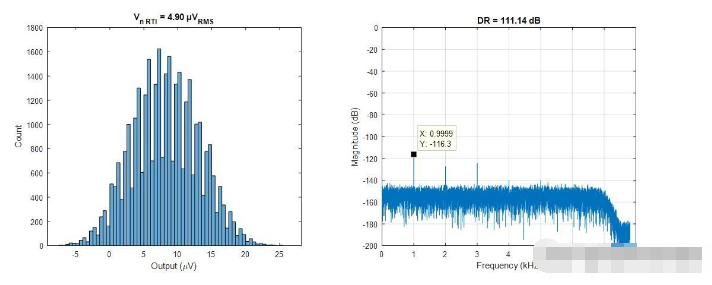

正如预期的那样,EVM在为所有三个ADC电源引脚使用干净的电压供应时表现最佳。图2显示了这些条件下的噪声直方图(左)和快速傅立叶变换(FFT)(右),得到的动态范围为113.56 dB,非常接近数据表规范。

图2AVDD、LVDD上清洁电源的噪声直方图(左)和FFT(右),和DVD光盘

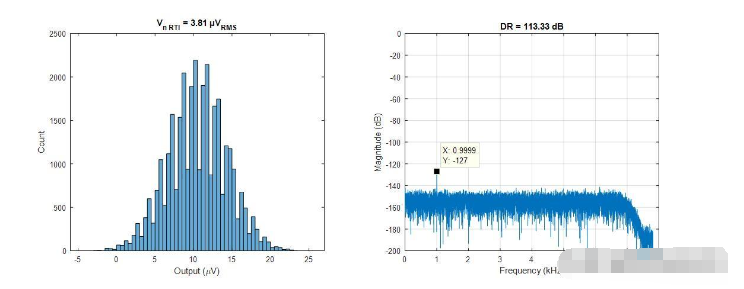

然后,我们在3-V AVDD电源上添加了1-kHz,100 mVP正弦波。该正弦波模拟电源噪声,并使用直流偏移等于标称AVDD电源电压(3v)的信号发生器应用于ADC。在这种情况下,ADS127L01上的内部LDO仍然能够抑制大部分噪声,并将标称性能保持在113.33 dB,如图3所示。请注意,在1kHz的频谱中出现了一个小音调,幅度为-127dB。这应该与原始输入信号电平(相对于满标度(-28 dB,对于2.5 V ADC参考电压)减去AVDD PSRR,或大约100 dB)相关。

图3噪声直方图(左)和FFT(右)用于LVDD和DVD光盘,AVDD上的涟漪

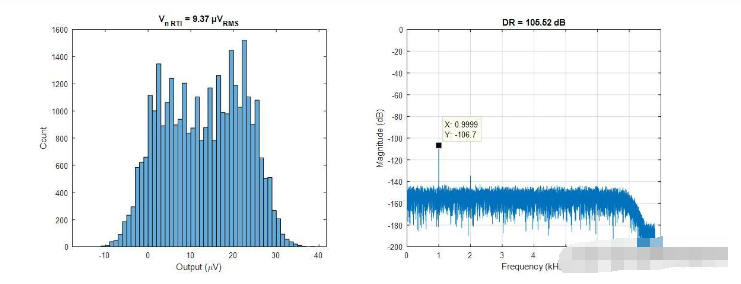

在下一次测试中,我们使用EVDD供电,而在下一次测试中,我们使用EVDD供电,并恢复为EVM供电。在这个测试中,我们输入一个以1.825伏直流偏移为中心的1千赫兹,100毫伏正弦波纹波,并绕过内部LDO。因此,如图4所示,LVDD电源噪声导致噪声性能显著降低(105.52 dB)。此外,与图3中的右侧图像相比,1 kHz音调在频谱(-106 dB)中更为明显。

图4噪声直方图(左)和FFT(右)用于AVDD和DVD上的清洁电源,纹波在LVDD上

在上一次测试中,我们将AVDD和LVDD恢复为默认的clean EVM电源,并将正弦波应用于DVDD。在这个例子中,纹波以1.8kHz为中心。有趣的是,与LVDD实验(111.14db)相比,图4显示了更小的动态范围退化,即使在产生的FFT中可以看到更多的1khz纹波谐波。

图5噪声直方图(左)和FFT(右)用于AVDD和LVDD上的清洁电源,纹波开启DVD光盘

最终,这些实验证实了图1中的结果,同时重申了某些电源(尤其是为delta-sigma调制器供电的电源)比其他电源更容易受到电源噪声的影响,可能需要特别小心才能保持较高的PSR。

提高PSR为此,让我们考虑几种使用三种不同技术在系统中保持良好PSRR的方法,首先从最关键的:布局开始。

优化布局布局优化是迄今为止您可以用来提高PSRR和保持系统性能的最重要的技术。由于我们已经花了大量时间讨论直流/直流开关稳压电源的噪声耦合,一个具体的布局优化行动,你可以采取的是隔离这种噪声开关稳压器远离敏感的模拟输入。开关调节器的效率很高,但它们可以在电源上注入大量瞬态电流,耦合到周围的电路中,包括ADC本身。如果功率调节电路与数字元件位于印刷电路板(PCB)的同一侧,则任何一个有噪声的回流电流都不应该流过更灵敏的模拟电路。

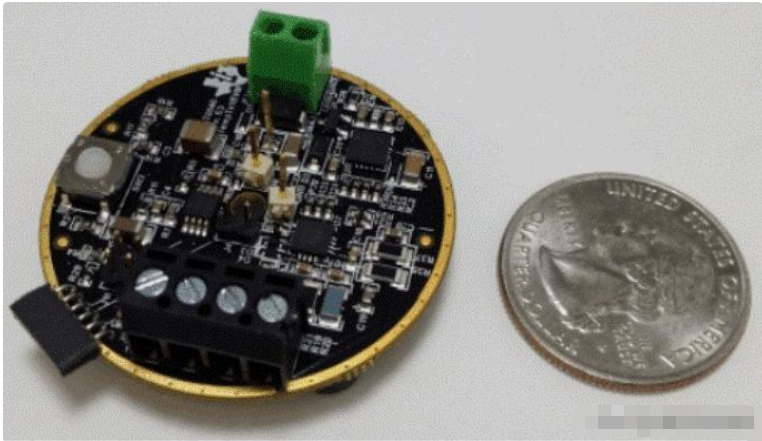

然而,有些印刷电路板可能受到其尺寸或形状的限制,使得这些类型的布局技术不可行。例如,图6显示了一个PCB的比例尺与TI的四分之一相比温度变送器参考设计. 在如此有限的空间内,优化布局可能是一个挑战。

图6温度变送器PCB与四分之一比较(TIDA-00095)

在这些情况下,以及所有PCB布局,都要确保始终使用正确的电源去耦。去耦电容器主要分为两大类:整体式和局部式。大容量去耦电容器通常直接放置在电源的输出端。这些电容器有助于过滤电源输出,并在负载电流波动时保持电压稳定。此外,大多数有源元件将需要至少一个本地去耦电容器直接挨着每个主电源引脚。

本地电容器通常比大容量电容器小一个数量级,用于提供设备的瞬时电流需求,同时滤除高频噪声。如果对给定的电源引脚建议使用多个去耦电容器(例如,0.01µF与1µF并联),请将较小的电容器放置在离电源引脚最近的位置。

此外,在第11部分中,我们讨论了某些有源元件(如时钟)可以在电源上引入大的瞬态。您可以通过使用额外的去耦元件(如串联铁氧体磁珠)来抑制这种噪声。

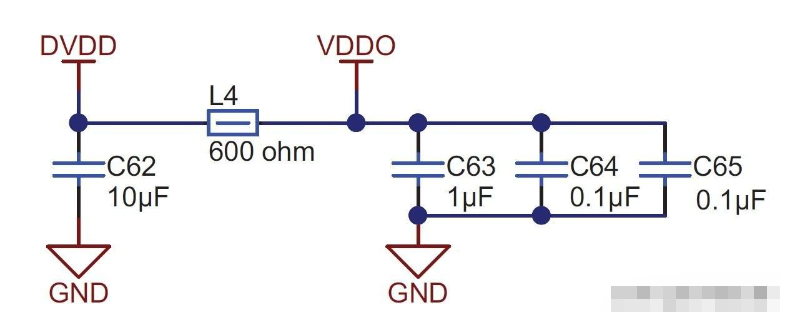

图7显示了ADS127L01 EVM示意图的一部分,以及ADC和时钟扇出缓冲电源使用的一些额外的去耦组件。扇出缓冲器必须参考与ADS127L01数字核心(DVDD)相同的数字输入/输出电平,这可能允许开关瞬态耦合到该电源上。为了保持系统性能,EVM使用电容器和铁氧体将DVDD与扇出缓冲输出电源(VDDO)分离。

图7ADS127L01EVM原理图上的ADC数字电源(DVDD)和时钟缓冲输出电源(VDDO)的去耦元件(电容器和铁氧体)

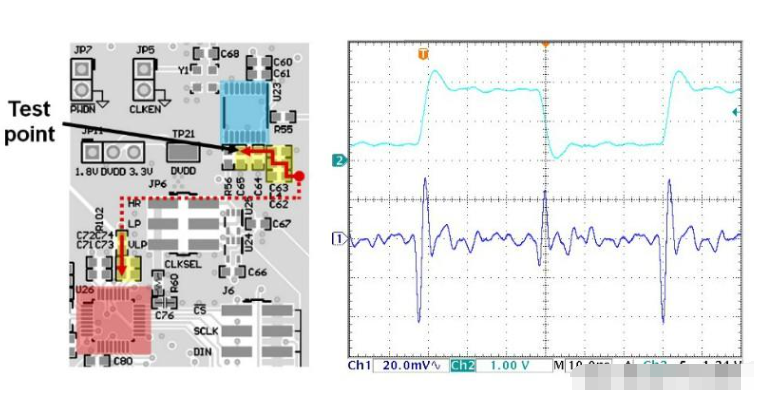

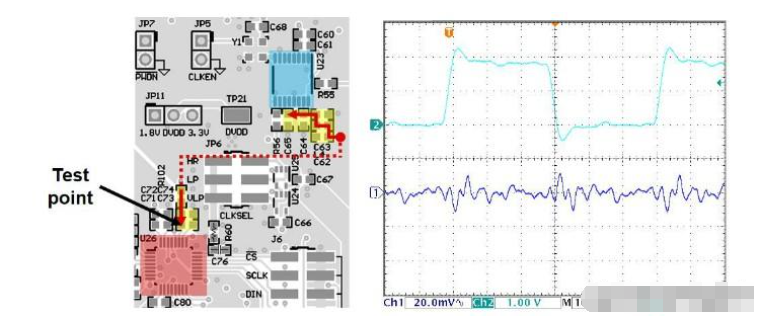

巧合的是,我们之前在第10部分讨论了ADS127L01 EVM的时钟扇出缓冲器及其时钟电路。在那篇文章中,我们展示了EVM的时钟电路,并用蓝色突出显示扇出缓冲器,用红色突出显示ADC。图8(左图)显示了具有相同突出显示的相同图像,不过现在我们也用黄色突出显示了去耦组件,红色箭头跟踪到IOVDD供应的dvd供应路径。

图8的左侧显示了IOVDD电源引脚处的测试点,而右侧显示了示波器在该点(Ch1)采集的电压。这个屏幕截图展示了由于输出时钟信号(Ch2)的每个上升和下降沿,缓冲器产生的大的电源瞬态,如C65所示。

图8ADS127L01EVM原理图(左)和缓冲器测试点的电压测量(右)

如果没有图7所示的去耦电路,图8右侧所示的瞬态将耦合到DVDD上并影响ADC的性能,与图5中的结果类似。然而,适当的去耦可确保这些故障被控制在时钟扇出缓冲器的输出中。图9中的右图显示了图9左侧所示的测试点(C73)处的示波器捕捉,可以明显看出这种抑制作用。请注意,图8中所示的瞬态有效地从图9中的示波器捕捉中消除,从而使到达ADC的电源噪声非常小。

图9ADS127L01EVM示意图(左)和ADC测试点的电压测量(右)

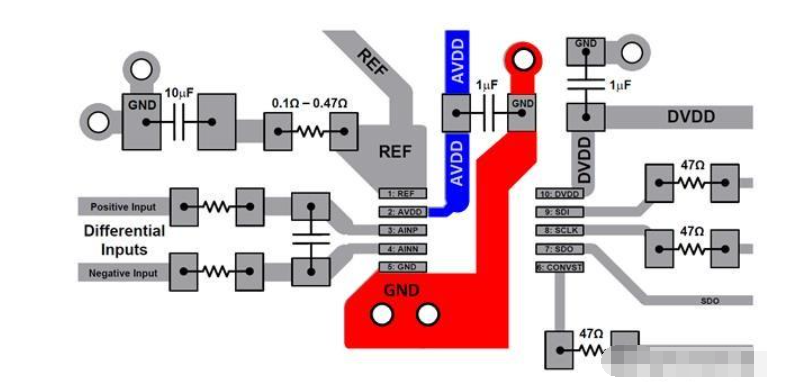

布线是您应该考虑的另一种布局技术,以保持低电源噪声。您应该始终将电源线穿过电容器的电极,然后尽可能地将电源线布线到设备引脚。此外,对于可能携带更大电流的电源,应使迹线更粗。别忘了地面也是一种补给。接地作为信号和电源的电流返回路径。使用带有额外通孔的大型地面浇注或平面可降低回路电感,并允许回流电流轻松返回电源。图10展示了其中一些概念。

图10布线技术,包括粗线和通过电容器垫布线

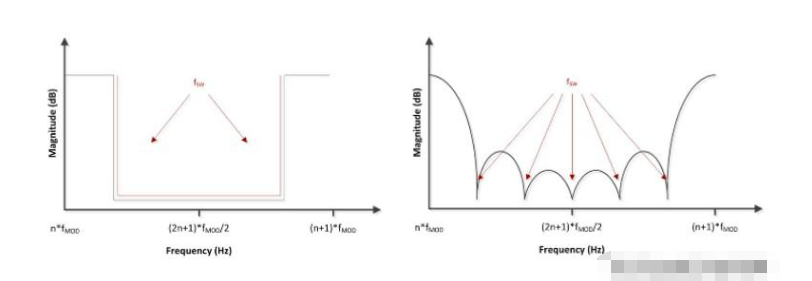

另一种可以用来降低电源噪声的技术是频率规划,无论是开关调节器还是ADC。如第11部分所讨论和图1所重申的,ADC在每种电源上可以表现出不同的PSRR特性。此外,所有ADC电源在数字滤波器阻带内的频率下,PSRR将大幅提升(见图1)。在delta-sigma adc中,数字滤波器响应以调制器频率(fMOD)的倍数重复。因此,如果开关噪声恰好落在调制器频率或其任何倍数附近,则开关噪声仍可能混入ADC通带。

如果可能的话,选择一个开关频率,使之成为滤波器的一个零值(通常是输出数据速率的倍数),以防止这些信号产生混叠并提高系统的PSR。图11说明了常见ADC滤波器类型的阻带:宽带有限脉冲响应滤波器(图11左侧)和sinc滤波器(图11右侧)。由于ADC数据速率通常由系统要求确定,红色箭头突出显示的区域是基于数字滤波器响应的开关频率的建议频带。如果您的数据速率是灵活的,但您的开关频率是固定的,请考虑选择您的ADC的输出数据速率,以便它在这个频率创建一个空值。

图11建议使用平通带(左)和辛基(右)过滤器

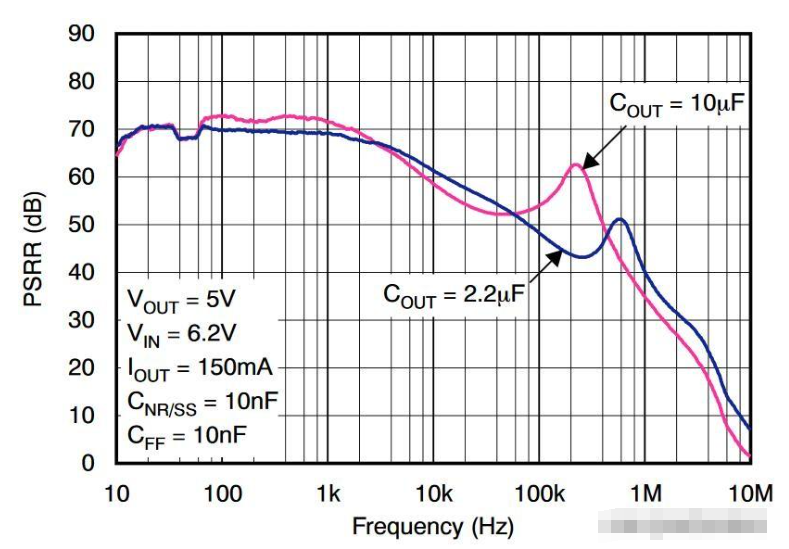

正如我们在本文第一节中讨论的,您可以通过添加LDO来抑制不需要的噪声来进一步提高系统的PSRR。如果您打算在您的系统中使用开关电源,您还应该考虑在您的系统中最有效的特定开关频率。该技术可用于所有高分辨率ADC应用,但对于更宽带宽的应用(噪声更可能耦合或混叠到输出中)来说,这一技术最为重要。在这些情况下,选择一个对你计划使用的开关频率具有最大电源抑制的LDO。或者反过来,考虑一个开关频率,它适合于你的LDO的PSRR曲线的最高部分。

图12显示了TI的PSRR与频率曲线图TPS7A49型LDO公司。注意,随着开关频率的增加,该LDO的PSRR降低。

图12TPS7A49 LDO,C的PSRR与频率曲线图出去= 2.2µF

如何预防和调试电源问题

在检查ADC的电源设计时,可以先验证几个参数,以排除任何潜在问题并确保首次通过成功。检查输入/输出的关键部件的电源/输出范围。一定要考虑到共享电源的所有活动组件的总电流消耗,并为额外的净空做预算。

此外,检查电源输出的最大电容负载,因为该电源上的所有大容量和局部去耦电容器都有效地并联在一起,并且可以很快相加。电容过大可能导致启动时间变慢。

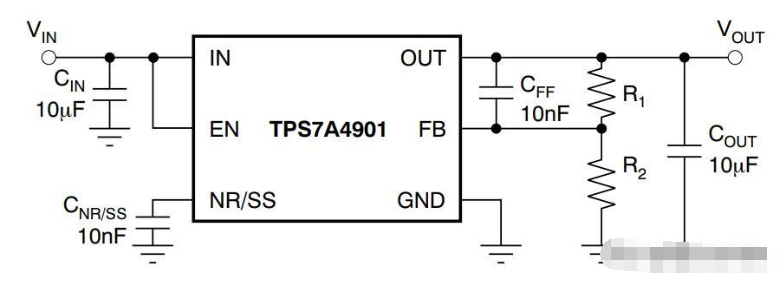

最后,检查LDO在输入和输出之间是否至少具有最小的压降电压,并考虑添加任何其他推荐的降噪(CNR)或前馈(CFF)电容器以进行附加滤波,如图13所示。

图13LDO上的滤波电容器

一旦确认电源设备配置正确,就可以通过增加ADC去耦电容器的大小来提供额外的滤波来提高整体噪声性能。这不仅对主电源管脚很有帮助,而且对连接到专用管脚进行外部解耦的任何内部电压节点都有帮助。ADC制造商通常也可以推荐电容值。请记住,将较小的电容器与较大的电容器并联放置,以获得最佳性能。

最后,如果您认为电源调节组件本身正在向ADC频谱中引入一个或多个音调,请尝试用外部工作台电源替换每个ADC电源,一次一个。如果这不能揭示问题,您也可以尝试更换主板的主电源,以确定噪声来自何处。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。