之前收到很多关于走线阻抗以及如何计算正确走线尺寸以达到可制造 PCB 中特定阻抗的问题。与确定单端走线的适当走线宽度一样重要的是确定差分对中两条走线之间的适当间距。所以问题是,差分对中的走线需要彼此靠近多近,“紧密耦合”的需求真的有必要吗?

该设计指南的有趣之处在于,它可能是唯一定义最差的 PCB 设计经验法则。数字意义上的“松耦合”或“紧耦合”究竟是什么?如果你问 10 位不同的信号完整性专家,你会得到 20 种不同的答案!

在本文中,我们希望在差分对间距方面更接近于紧耦合与松耦合的真实描述,以及差分对间距如何影响阻抗、差模噪声、共模接收噪声和终止。正如我们将看到的,关注紧耦合(无论它是什么意思)有其优点,但由于错误的原因,它经常被认为是必要的。

差分对间距如何影响信号完整性让我们看一下我上面提到的每个维度,以确切了解差分对间距在何处起作用,以及如何设置适当的值。

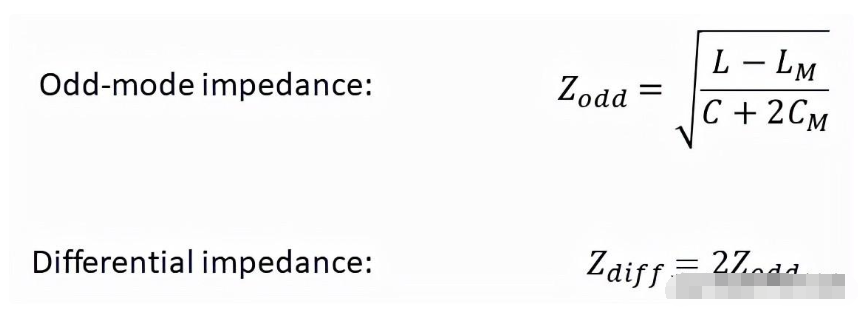

阻抗差分对中受间距影响的主要参数是阻抗。差分对的阻抗取决于每条走线的自电容和自感,以及每条走线之间的互电容和互感。这意味着不同 l 对的典型阻抗公式需要分解为奇数阻抗和差分阻抗,其定义如下:

奇模和差模阻抗公式。

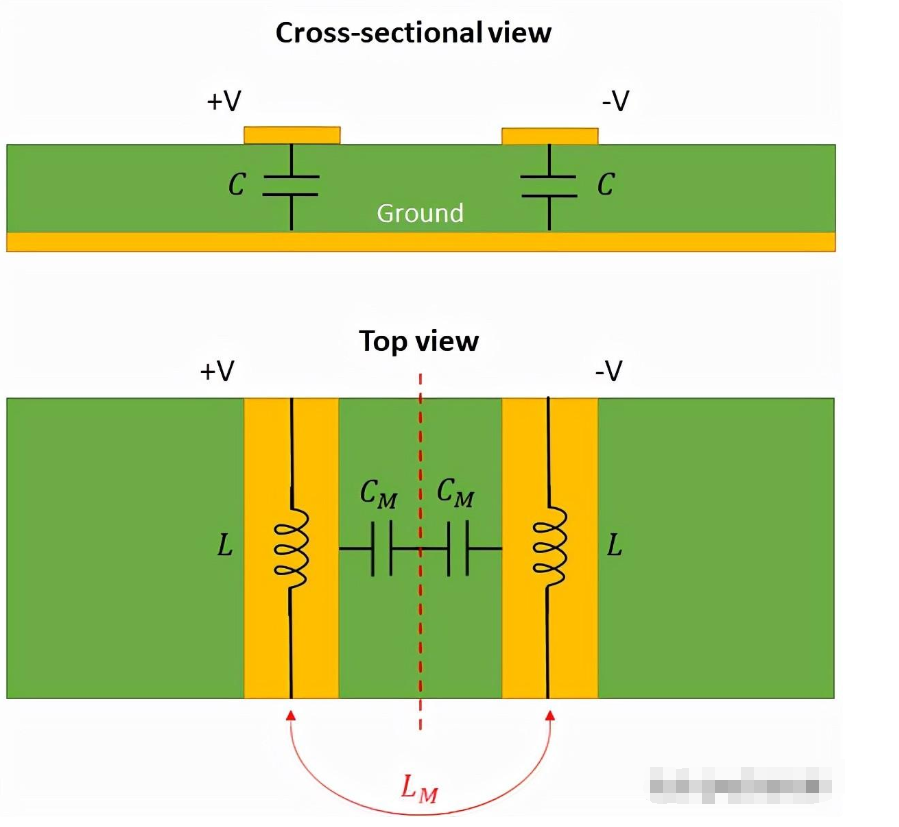

互感和电容的存在使两对分别具有等效的总电感和电容。在上面的方程中,我们忽略了损耗(传输线阻抗方程中的 R 和 G),但没关系,这里的重点是注意间距。

差分对中的两条走线之间存在互感和电容。

将线对放置得越近,差分阻抗越小,因为L M和C M变大。既大号中号和Ç中号收敛于零间距趋于无穷。

换句话说,如果您的设计是为了达到差分阻抗目标(例如标准中指定的或根据测量确定的),那么您不能将两对靠得太近,否则您将不会违反阻抗目标作为差分阻抗会太小。但是,较小的间距会使沿路径长度的两条迹线之间的电场和磁场集中,从而增加损耗。

两条走线之间的互感和互电容不容易计算,也没有简单的封闭式公式可以使用。一些研究文章中有一些较长的公式,但它们非常长且笨拙。更好的选择是使用带有内置计算器的叠层编辑器。此类实用程序通常使用电磁场求解器来确定差分对的阻抗,而不是确定互电容和电感。

共模噪声抑制差分对有时被描述为不受串扰影响,尽管并不总是说明这是来自单端信号还是差分信号。无论如何,事实是差分对无法避免来自差模噪声源或共模噪声源的串扰。要了解有关前者的更多信息,您可以阅读这篇关于差分串扰的文章。

源自串扰的共模噪声呢?如果您正在查看在附近的差分模式对中引起信号的单端干扰走线,现实情况是您永远无法保证完全抑制共模噪声,无论您在差分模式中将两条走线走多近一对。然而,更紧密的耦合确实有帮助。

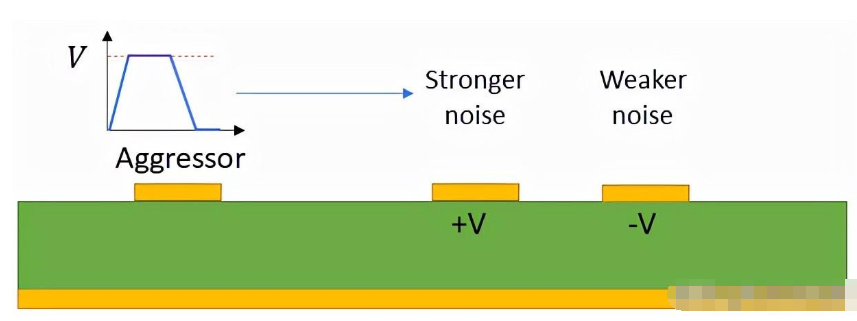

要了解原因,我们只需要看看来自单端侵略者轨迹的场是如何在空间中传播的。由于场随着与走线的距离而下降,差分对中较近的走线比较远的走线接收到更多的噪声。

干扰源走线辐射的场随着距离的增加而减弱,因此差分对中每条走线接收到的噪声可能不相等,并且无法被差分接收器完全消除。

在这里,我认为最佳解决方案是将单端走线从差分对移得更远,而不是仅仅将差分对放置得更近一些。如果这不是一个可行的解决方案,那么较小的间距将产生相同的效果,但沿差分对的损耗更高。

差模 EMI还有一种说法是差分对不**** EMI。这也是不真实的;如果这是真的,那么我们将无法测量差分串扰。然而,来自差分对的辐射 EMI 处于差分模式,因此它不如从单端走线或一组走线发出的噪声强。这就是您可以在差分链路上运行极高速串行数据而不会经常失败 EMC 测试的原因之一:与通过单个迹线发送数据时所看到的噪声相比,噪声要小得多。

由于差分 EMI 仅在通过长差分对路由串行数据时才会成为问题,因此您可能会想将差分对靠得更近以抵消噪声。我要再次声明,在这种情况下,损失(插入损失)更为重要。在需要使用差分对的长链路中,损耗将主导通道行为,因此最好选择更大的间距。如果开始时通道设计正确,即使数字比特流的上升时间极快(低于 10 ps),也不应该出现极端的辐射噪声问题。

为什么要关注间距和长度匹配?在遥远的过去,在设计师可以使用丰富的 CAD 工具和专业的电子设计软件之前,将长度匹配和一致的间距应用于差分对是一个耗时的过程。今天,PCB 设计人员被 CAD 工具宠坏了,这些工具使得将长度匹配部分应用到差分对变得非常容易。与布线工具接口的设计规则还可以非常轻松地在差分对中的每条迹线之间应用一致的间距,如果需要,包括非常紧密的间距。

尽管在传统端接方法和差分阻抗目标的范围内可能没有必要,但我们看到使用小间距的几个原因:

降低差模噪声****和差分串扰

将噪声作为真正的共模噪声接收的几率更高

线对之间发出的差模噪声较低

然而,与普遍的看法相反,选择尽可能小的间距并不是终止所必需的,它会增加沿线对长度的损耗。终止是一个很长的讨论,我将在一些视频和另一篇文章中介绍。可以在本文中找到概述,主要内容是端接将差分对视为两个单端信号,而不是某些差分阻抗。

当您需要在设计中设置和维护差分对间距和特定阻抗目标时,几大知名的EDA厂商,都会提供完整的 PCB 布线和仿真功能,目前使用的AD就比较好用。集成布线工具为您提供完成物理布局所需的一切,同时保持几何规则和阻抗目标。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。