在您的下一个 PCB 设计过程中,有几个因素会影响走线宽度、长度和样式。PCB原型. 本文将深入探讨需要特定走线布局特性的各种应用,以及如何或何时将它们纳入您的 PCB 设计。

什么是走线宽度?让我们从基础开始。究竟什么是走线宽度,为什么指定特定的走线宽度如此重要?PCB 走线的目的是将任何类型的电信号(无论是模拟、数字还是电源)从一个结点连接到另一个结点。

结点可以是组件的引脚、较大迹线或平面的分支,或者是用于探测的空焊盘或测试点。走线宽度通常以密耳或千英寸为单位。普通信号的标准走线宽度(无特殊要求)可能在 7-12 mil 范围内,长达几英寸,但在定义走线的宽度和长度时,应考虑许多因素。

应用程序通常会决定 PCB 设计中的走线宽度和类型,并且在某个点上,通常会在PCB制造成本、电路板密度/尺寸和性能。如果电路板具有特定的设计要求,例如速度优化、噪声或耦合抑制或高电流/电压,则走线宽度和类型可能比优化裸 PCB 的制造成本或整个电路板尺寸更重要。

PCB 制造中与迹线相关的规范作为一般规则,以下与跟踪相关的规范开始推高裸 PCB 制造成本。

由于更严格,成本变得相当高印刷电路板公差以及制造和生产所需的高端设备检查或测试 PCB:

走线宽度小于 5 mils (0.005”)

走线间距小于 5 密耳

通过直径小于 8 密耳的孔

走线厚度比 1 盎司(相当于 1.4 密耳)更薄或更厚

差分对和受控长度或走线阻抗

包含 PCB 封装(例如极细间距 BGA 或高信号数并行总线)的高密度设计可能需要细至 2.5 密耳的走线宽度和特殊类型的通孔,例如直径为 6 密耳或更小的激光钻孔微通孔。相比之下,一些高功率设计可能需要非常大的走线或平面,占用整个层,并且比标准的盎司更厚。空间受限的应用可能需要包含多层的非常薄的电路板和半盎司(0.7 密耳厚)的有限覆铜厚度。

在其他一些情况下,从一个外围设备到另一个外围设备的高速通信设计可能需要具有受控阻抗和特定宽度和间距的走线,以最大限度地减少反射和电感耦合。或者设计可能需要一定的长度以匹配总线中的其他相关信号。高压应用需要某些安全功能,例如最小化两个暴露的差分信号之间的距离以防止电弧放电。无论是什么特性或特性,轨迹定义都很重要,所以让我们探索各种应用。

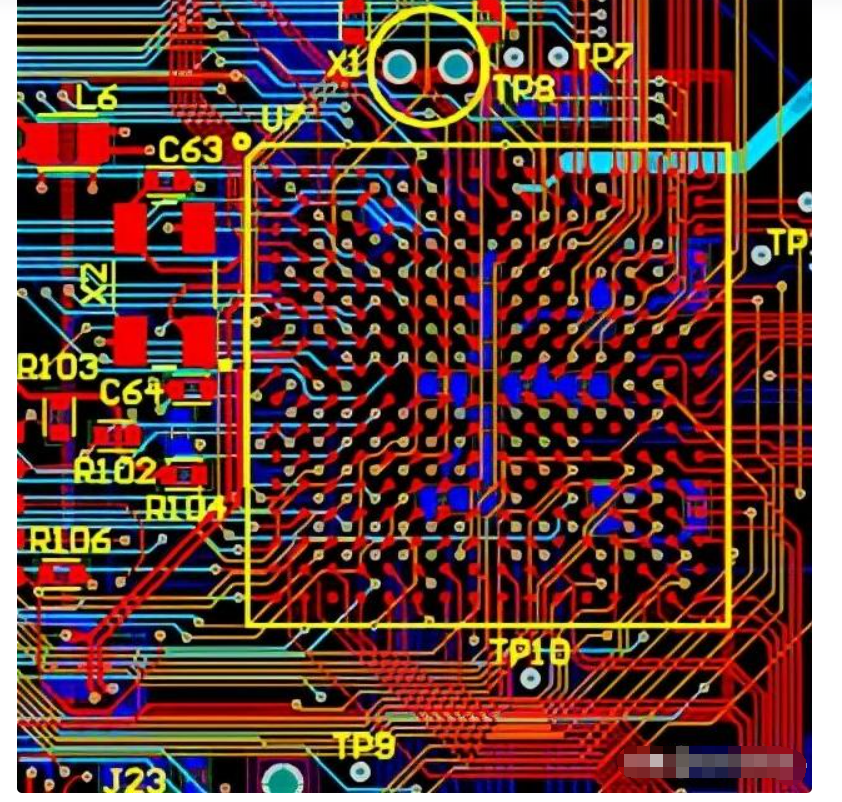

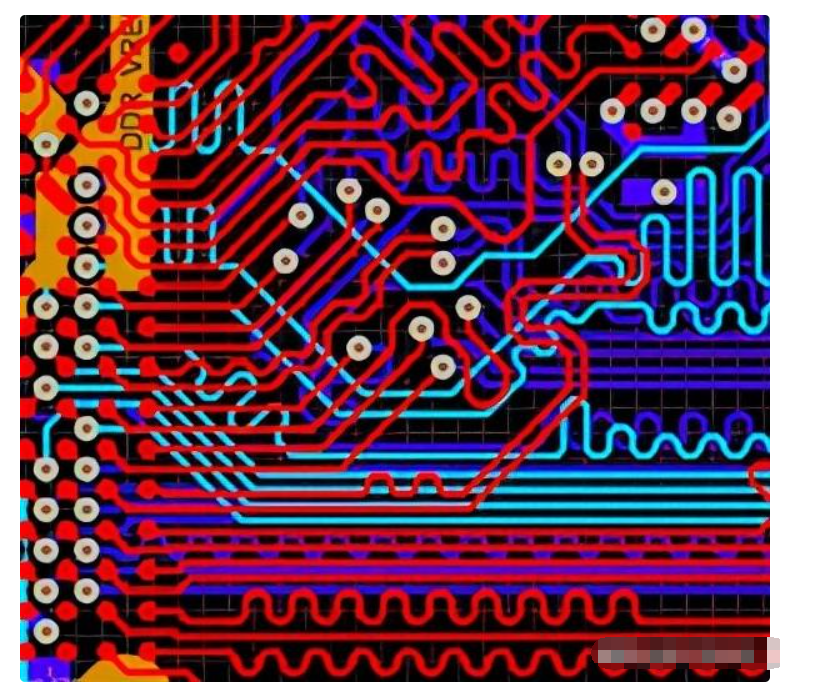

各种走线宽度和厚度PCB 包含多种走线宽度是很常见的,因为它们取决于信号的需要(如图 1 所示)。所示的较细迹线用于通用 TTL(晶体管-晶体管逻辑)电平信号,对大电流或噪声保护没有特殊要求。

这些将是电路板上最常见的走线类型。

图 1. 包含不同走线宽度和类型的 4 层板示例

较粗的走线已针对载流能力进行了优化,用于需要更高功率的外围设备或与电源相关的功能,例如风扇、电机和向较低级别组件的一般功率传输。甚至图中左上角还显示了一个差分信号(USB 高速),其特定间距和宽度定义为满足 90 欧姆阻抗要求。图 2 显示了一个稍微密集的 6 层板和一个 BGA(球栅阵列)组件,需要更细的走线。

包含 256 引脚 BGA 组件且走线宽度为 5 密耳的 6 层板示例

PCB走线宽度是如何计算的?让我们来看看为将电流从一个电源组件传输到外围设备的电源信号计算特定走线宽度的过程。在本例中,我们将计算用于直流电机的电源路径的最小走线宽度。电源路径从保险丝开始,穿过 H 桥(用于管理直流电机绕组上的电力传输的组件),并在电机连接器处结束。直流电机所需的平均连续最大电流约为 2 安培。

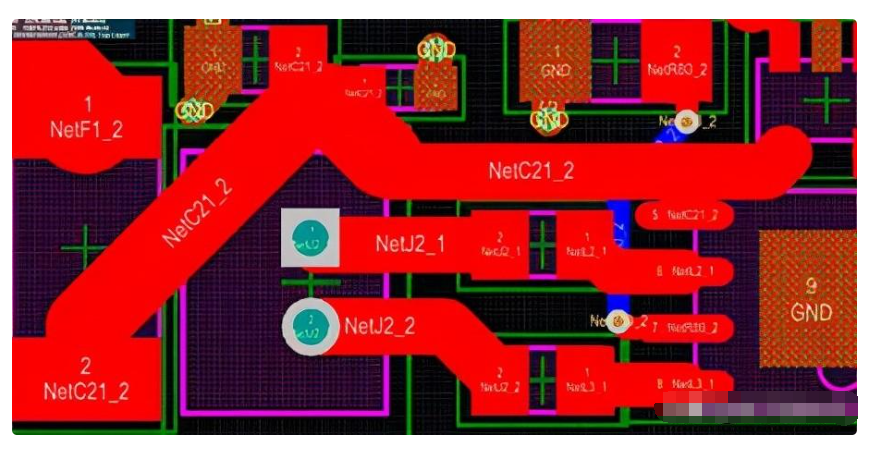

现在,PCB 走线充当电阻器,走线越长越窄,增加的电阻就越大。如果没有正确定义走线,高电流可能会损坏走线和/或给电机带来显着的电压降(导致速度变慢)。图 3 中所示的 NetC21_2 长约 0.8 英寸,最大需要承载 2 安培。如果我们假设一些一般情况,例如正常操作期间 1 盎司的铜浇注和环境室温,我们就需要计算最小走线宽度和该宽度下的预期电压降。

直流电机电源路径的优化走线宽度示例

如何计算PCB走线电阻?以下是用于跟踪面积的公式:

面积[mils²] = ( Current[Amps] / (k*( Temp_Rise[°C] )^b) )^(1/c)其中对于外部(或顶部/底部)层遵循 IPC 指南,k = 0.048, b = 0.44,c = 0.725。请注意,我们真正需要在此处插入的唯一变量是 current。

在下面的等式中使用这个区域将为我们提供必要的宽度,它告诉我们我们的走线需要多宽才能承载电流而不会出现任何潜在问题:

宽度[mils] = 面积[mils^2]/(厚度[oz]*1.378[mils/oz])其中 1.378 与标准的 1 盎司浇注厚度相关。

通过在上面的计算中插入 2 安培,我们得到大约 30 密耳的最小值。

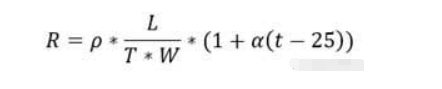

但这并没有告诉我们电压降是多少。这有点复杂,因为它需要计算走线的电阻,可以根据图 4 中所示的等式进行计算。

图 4. PCB 走线电阻公式

在这个公式中,ρ = 铜的电阻率,α = 铜的温度系数,T = 走线厚度,W = 走线宽度,L = 走线长度,t = 温度。如果将所有相关值插入 0.8 英寸长、30 密耳宽的走线,我们发现走线电阻将在 0.03 左右?并将电压下降约 26mV,这对于应用来说已经足够了。了解是什么影响这些值会很有帮助。

对于具有高速通信的数字设计,可能需要特定的间距和调谐长度以最大限度地减少串扰、耦合和反射。这方面的一些常见应用是基于 USB 的串行差分信号和基于 RAM 的并行差分信号。通常,USB 2.0 需要 480Mbit/s(USB 高速等级)或更高速度的差分对路由。部分原因是高速 USB 通常在低得多的电压和差分下运行,从而使整体信号电平更接近本底噪声。

有布线高速 USB 线时要考虑的三个重要事项:走线宽度、走线间距和走线长度.

所有这些都很重要,但三者中最关键的是确保两条走线的长度尽可能匹配。作为一般经验法则,如果走线彼此之间的长度相差超过 50 密耳(对于高速 USB),则会显着增加反射风险,从而导致通信不良。90 欧姆匹配阻抗是差分对布线的常见规范,为此,应优化走线的宽度和间距。

图 5 显示了为高速 USB 接口布线的差分对示例,其中包含 15 mil 间距的 12 mil 宽走线。

图 5. USB2.0 高速的差分路由

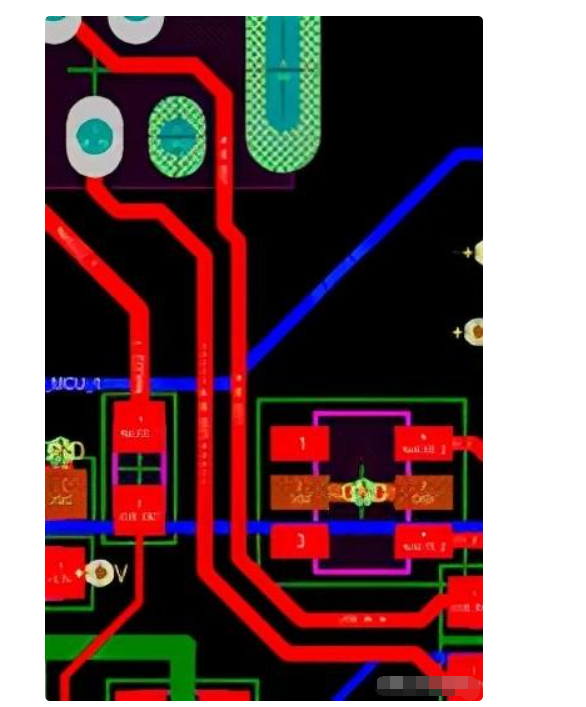

包含并行接口的基于存储器的组件的接口,例如 DDR3-SDRAM,在走线长度方面将受到更严格的限制。最高档PCB设计软件将具有长度调整功能,可优化走线长度以匹配并行总线中的所有相关信号。图 6 显示了具有长度调谐走线的 DDR3 布局示例。

图 6. 长度调整的 DDR3 内存走线示例

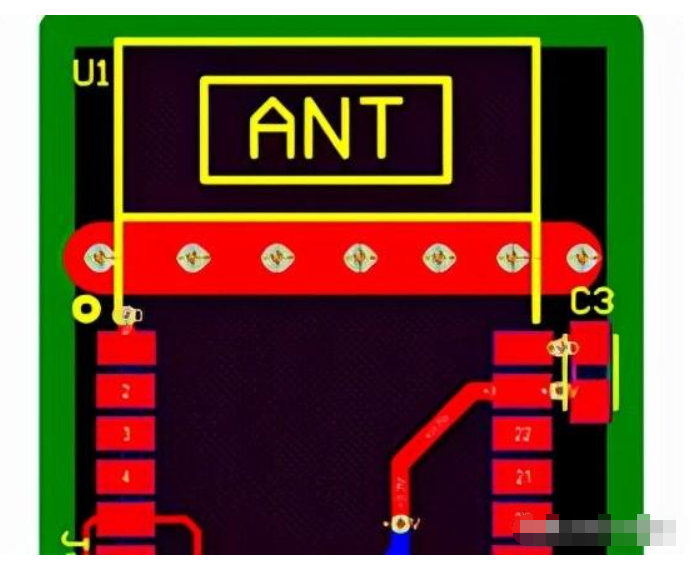

地面填充痕迹和平面一些带有噪声敏感元件的应用,例如无线芯片或天线,可能需要一些额外的保护。设计带有嵌入式接地过孔的走线和平面可以极大地帮助最大限度地减少附近走线或平面拾取的耦合以及潜入电路板边缘的板外信号。

图 7 显示了一个示例蓝牙模块将其天线(通过丝印“ANT”标记)放置在电路板边缘附近,位于包含连接到接地平面的嵌入式通孔的粗走线外侧。这有助于将天线与其他板载电路和平面隔离。

图 7. 带有接地过孔嵌入式走线的蓝牙模块有助于抑制噪声

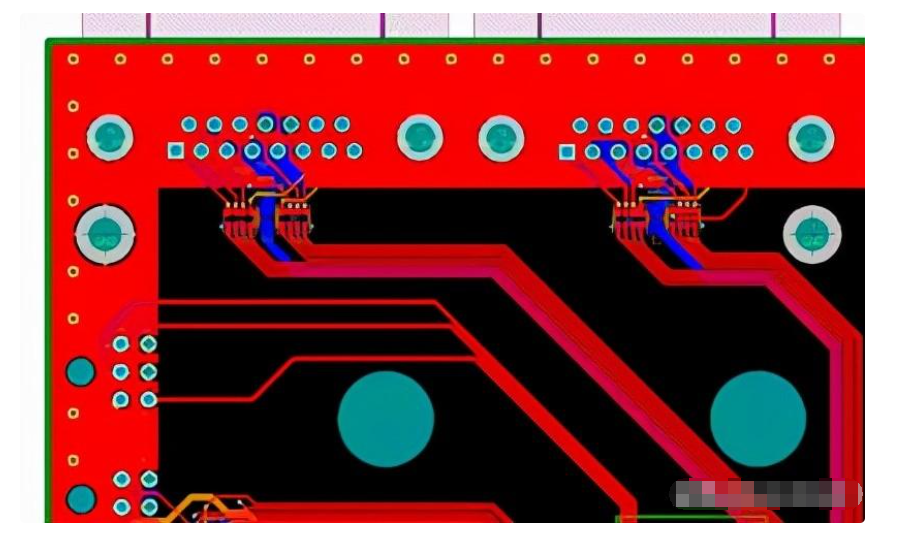

这种接地过孔嵌入迹线(或本例中的多边形平面)的另一种方法可用于保护电路板电路免受外部、板外无线信号的影响。图 8 显示了一个噪声敏感 PCB,沿着电路板的周边有一个接地过孔嵌入平面。

图 8. 带有过孔的接地平面衬在敏感的 PCB 上以防止板外干扰

PCB布线的最佳实践许多因素会影响 PCB 世界中的走线特性,因此在布线下一个 PCB 时一定要遵循最佳实践,您会发现 PCB 制造成本、电路密度和整体性能之间的平衡。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。