RF PCB 设计与传统电路板有些不同。使其与众不同的是阻抗匹配、走线类型(最好是共面)、消除通孔短截线(以避免反射)、接地层、通孔和电源去耦等参数。堆叠和材料选择等其他方面在这些电路板中也起着至关重要的作用。

RF PCB 设计与传统电路板有些不同。使其与众不同的是阻抗匹配、走线类型(最好是共面)、消除通孔短截线(以避免反射)、接地层、通孔和电源去耦等参数。堆叠和材料选择等其他方面在这些电路板中也起着至关重要的作用。

考虑到所有这些因素,射频设计过程的复杂性会因 EMI 干扰、高频信号通道等因素而增加。在本文中,我们将详细讨论所有这些问题。首先,让我们讨论阻抗匹配。

阻抗匹配在受控阻抗射频电路中,当整个迹线的阻抗保持相同时,从源到负载的最大功率传输不会失真。该阻抗称为迹线的特性阻抗(Z 0 )。特性阻抗取决于走线的几何形状,例如走线宽度、PCB 材料的介电常数、走线厚度以及距参考接地层的高度。为了匹配这些阻抗,还设计了匹配电路。

射频板材料RF PCB 采用满足高频操作要求的某些材料制造。这些材料应具有低信号损耗、在高频操作下保持稳定,并且应能够吸收大量热量。介电常数 (D K )、损耗角正切 (tan δ) 和热膨胀系数 (CTE) 值也需要在宽频率范围内保持一致。这些板的介电常数典型值范围为3 到 3.5。对于 10-30GHz 的频率范围,损耗角正切值在0.0022 到 0.0095 的范围内。

除了所有这些特定的必需品外,还考虑了材料成本和制造的便利性。

通常使用由聚四氟乙烯 (PTFE)、陶瓷和碳氢化合物制成的材料,这些材料相互混合或与一种玻璃混合。罗杰斯材料是射频电路板的常见选择。罗杰斯材料有不同的变体可供选择。下面列出了其中的一些:

RT/duroid

RO3000

RO4000

Rogers TMM

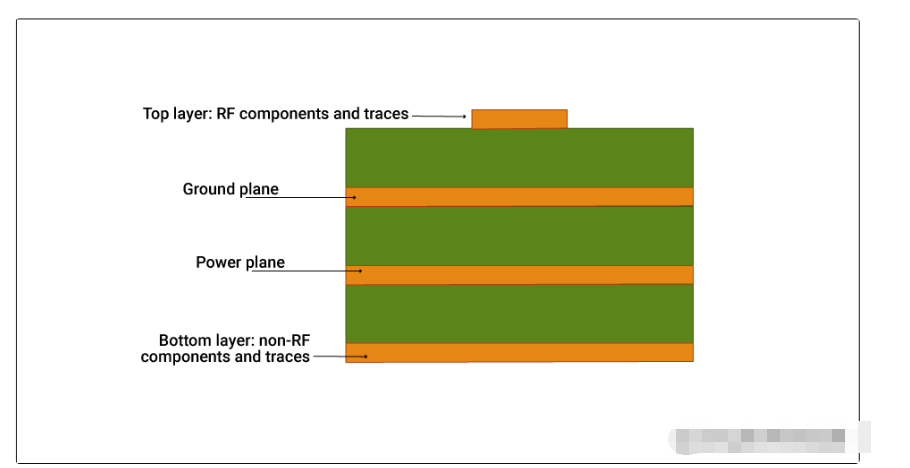

射频板叠层需要注意走线和元件之间的隔离、电源去耦、层数和排列、元件放置等细节。标准的 4 层射频叠层如下图所示。

4 层射频 PCB 叠层

射频元件和走线放置在顶层。该层紧随其后的是接地层和电源层。所有非射频元件和走线都填充在底层。这种安排在 RF 和非 RF 组件之间提供了最小的干扰。直接接地层为接地返回电流提供了最小路径。因此,总而言之,这是一个适用于小型射频板的叠层。

射频走线设计RF 走线传播高频信号,因此会受到传输损耗和干扰问题的影响。这些走线的特性阻抗是设计人员主要关心的问题。在射频板中,走线被视为传输线。设计的最常见的传输线类型是共面波导 (CPWG)、微带和带状线。以下是确定正确操作和最小损耗的射频走线设计方面:

走线的长度应尽可能短。这有助于减少衰减。

在布局中,切勿将 RF 走线和普通走线相互平行放置。如果这样放置,两者之间就会产生干扰。

需要接地层为信号提供返回路径。

测试点不应该放置在迹线上。它将中断走线的阻抗匹配值。

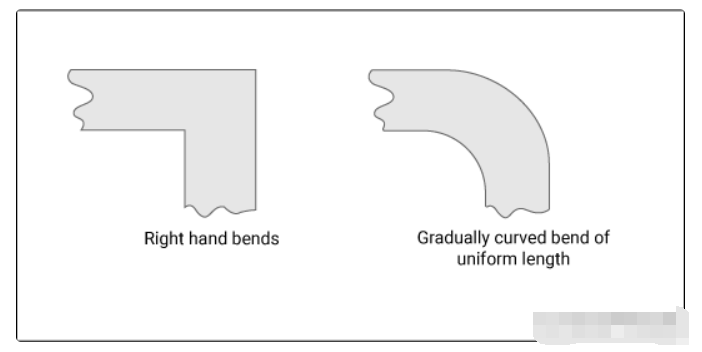

与保持急转弯相比,逐渐弯曲的弯道更适合跟踪性能。

右手弯和弯弯比较

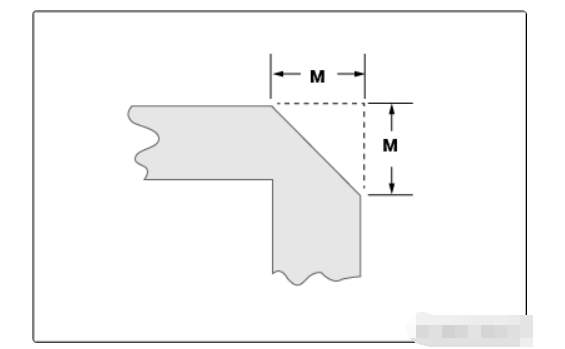

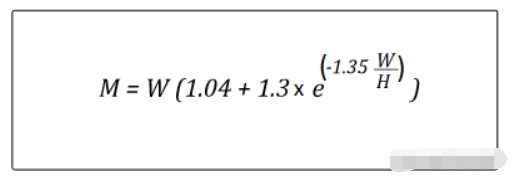

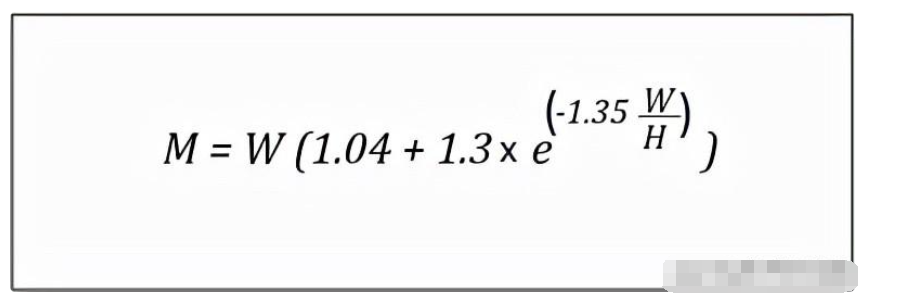

在无法避免右弯的情况下,使用计算来减少不良影响。走线的计算如下所示:

射频走线的计算

这里,M 由以下公式给出:

在 RF PCB 设计中查找计量尺寸的公式

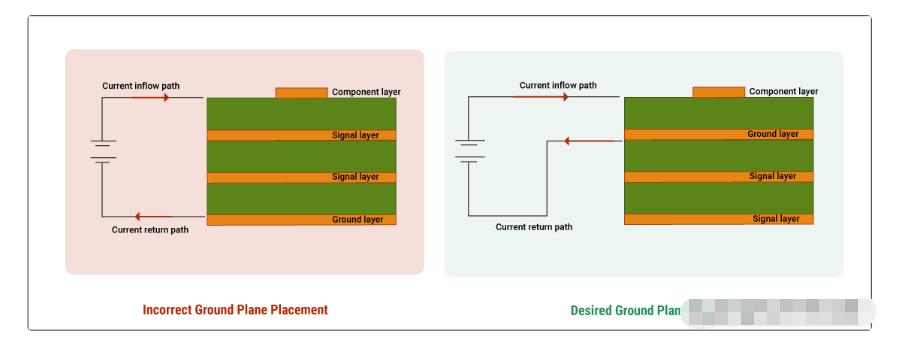

任何射频迹线或组件都需要电流通过它传播的返回路径。地平面负责这一点。然而,接地层需要一些额外的设计考虑。让我们来看看这些。

每个射频层都应该有一个专用的接地层。该接地层紧邻该层下方,以使电流流动路径最短。

RF PCB 中所需的接地层布局

地平面应该是连续的。不允许休息。这样的中断可能会为电流返回的更短路径铺平道路。

对于放置在射频传输线中的每个分流元件,至少需要两个接地过孔。

应尽可能避免射频走线中的过孔。但是,如果这些无法避免,则必须遵循特定的通孔直径和长度。通孔会在电路板中感应寄生电容。在射频板的情况下,该电容会影响高频操作。因此,为了减少这些频率的干扰,重要的是设计过孔时要牢记以下准则:

为了减少寄生电容,引入更多的平行过孔。

对于组件的每个引脚或焊盘,必须存在专用过孔。

在适用的情况下通过缝合实现接地层。这为电流建立了更短的接地返回路径。

减少通过过孔从一层到另一层的射频走线布线。

使用设计允许的顶层接地平面和内层平面之间的最大过孔数量。这些过孔的放置距离不应超过信号波长的 1/20。

对于射频板,降噪至关重要。在高工作频率下,这些板对噪声的影响变得非常敏感。因此,所有可能的方法都用于去噪。一种这样的方法称为电源去耦。

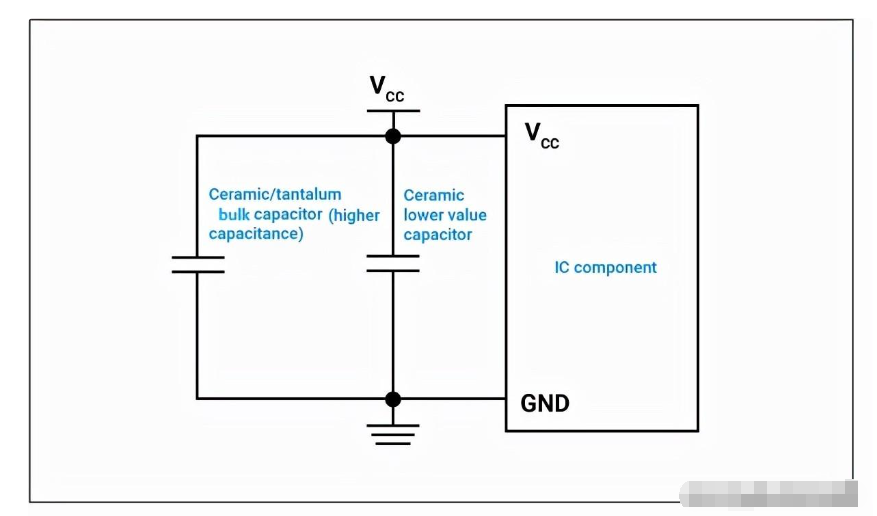

去耦电容的选择使用此过程过滤通过电源进入电路的噪声。为此指定的电容器称为去耦电容器。这些电容器跨接电源。

阻抗匹配是每个射频电路板不可或缺的特性。因此,连接去耦电容后,整个电路的阻抗应该不会发生变化。坚持以下设计注意事项以避免阻抗变化:

始终连接具有最小阻抗的电容器以进行去耦。

以自谐振频率 (SRF) 操作电容器以产生最小阻抗。电容器的 SRF 值与其电容值成反比。

选择 SRF 接近噪声频率的电容器。

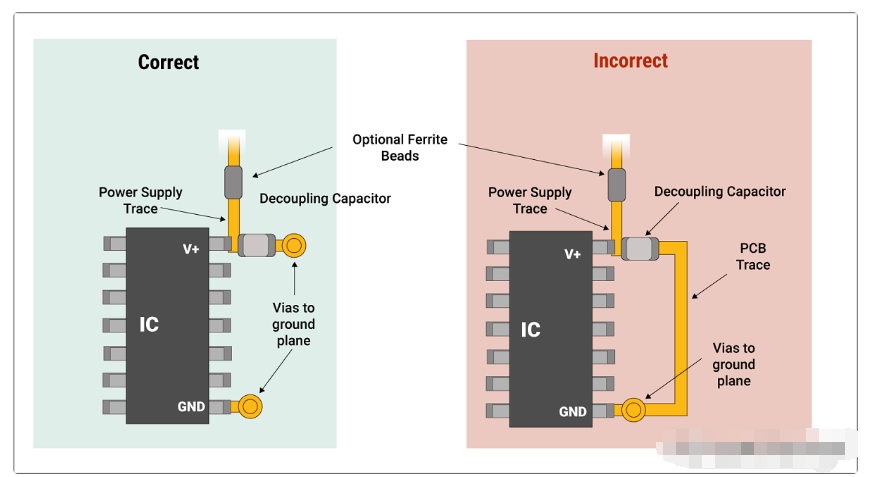

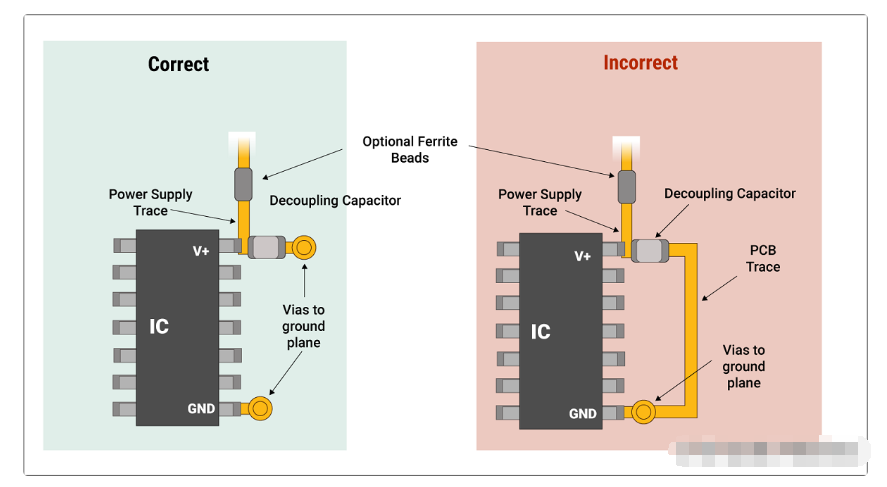

去耦电容的放置也是正确进行射频设计的重要部分。下面给出了一个简单的电路,该电路说明了两个与 IC 组件并联放置的去耦电容器。

射频元件的电源去耦

较高的电容器旨在过滤系统中的低频噪声并存储能量。高频噪声被下部电容滤除。其他与放置相关的指南是:

RF PCB 设计的电源去耦指南

去耦电容应放置在与元件相同的层上。

将电容器与信号流路径平行放置。

为每个电容器保留单独的接地过孔。

电容器应按其电容从电源的升序排列。也就是说,电容最小的那个离电源最近。

射频板的设计和制造需要设计师和制造商更多的关注。由于这些板子容易受到干扰和高频噪声,即使是最轻微的错误也会影响操作。以上所有方法和方面都将帮助我们更好地进行设计。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。